芯粒的基础知识

芯粒的基础知识

芯片集成方式

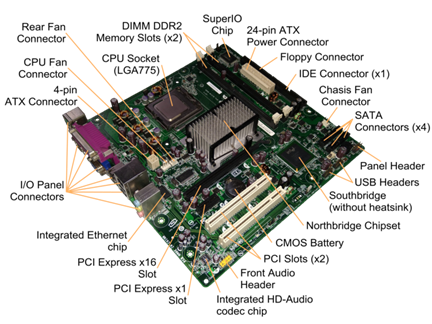

传统的芯片设计是分立式的,即将不同的功能模块(如 CPU、内存、输入输出接口等)作为独立的组件来设计和封装。这些组件通过主板上的线路或总线连接,形成一个完整的系统,类似于如下图所示的结构。每个模块都有独立的封装和互连,彼此之间通过物理线路连接。这种设计方案体积大、功耗高、通信延迟较大,且系统复杂,需要大量的外部连接和硬件支持。

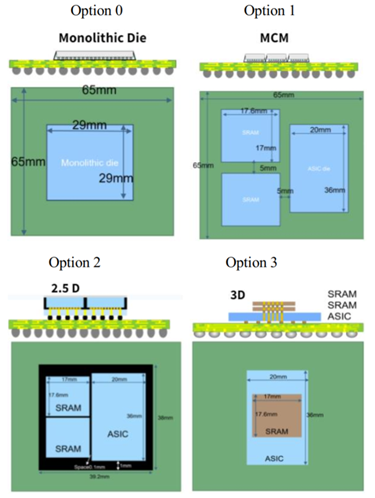

因此业界开始发展集成式的芯片设计方案,即将多个功能模块集成在一个芯片中,从而减小芯片间的数据传输距离,提高带宽以及模块之间的通信延迟。常见的集成化的芯片设计方式可以分成以下几种:单片式集成(Monolithic Die)、多芯片模块(Multi-Chpi Module,MCM)、2.5D集成(2.5D Integration)、以及3D集成(3D integration),如下图所示。不同于分立式设计将不同的功能模块制作成独立的芯片,然后通过电路板上的连接将这些芯片集成到一个系统中,单片式芯片将所有功能模块都集成在一个单一的大芯片中。由于所有功能模块都在同一个芯片上,其也需要使用同一工艺节点制造。目前方兴未艾的片上系统(System on Chip, SoC)本质上就是一个单片集成的芯片,将整个系统的核心功能(处理器、内存、I/O、通信模块、图形处理单元 GPU等)集成在同一个硅片上,形成一个完整的系统,在手机芯片里SoC架构有着广泛的应用。但随着芯片功能复杂化,单片芯片的面积增加,导致晶圆制造的良率下降,缺陷率提高,成本显著上升。目前普遍称单片集成芯片在发展上遇到了四堵墙的瓶颈:面积墙、存储墙、成本墙、功耗墙:芯片尺寸受光刻机曝光机最大尺寸限制(目前为32 x 26 mm = 832 mm2),无法持续增加芯片尺寸;计算芯片和片外存储芯片之间的带宽成为了限制性能提升的瓶颈;先进工艺和大尺寸芯片的良率下降使得先进工艺芯片单位功能的成本不降反升;大量晶体管发热,供电和散热复杂。另一方面,大芯片在温度不均会带来严重的应力问题,导致翘曲、可靠性下降。

业界为了克服单片集成的瓶颈给出的解决方案是:为了保证性能还是将不同的模块集成在同一个芯片里,但是将各个模块解耦开单独制造。此时不需要用同一工艺节点在同一个晶片上一起制造所有模块,而是可以分别制作各个模块后再通过集成方法将他们集成到一个系统中。这种设计方案降低了芯片设计中的耦合性,和软件工程的设计思想也很类似,实际上工程中的思想都是通用的。MCM就是这种设计思想驱动下的早期实现方式,MCM 将多个功能模块(例如 SRAM 和 ASIC Die)以平面方式组合在一个基板上。这些模块彼此独立制造,然后通过封装实现实现物理和电气连接。每个芯片模块可以用不同的工艺制造。比如逻辑模块可以用先进的工艺节点,而存储模块可以用成熟的工艺节点,从而降低整体成本。但在MCM方案中,模块之间还是通过传统的封装互连技术(如 C4 凸点)来实现信号传输,延迟和功耗略高于单片。此外MCM的封装占用空间较大,不适合高密度应用,一般用于功能模块明确、对延迟要求不高的系统设计,比如某些嵌入式设备或消费电子。

为了克服MCM信号延迟高、占用空间大等缺陷,业界又提出了2.5D封装的设计方案。在2.5D 技术中,芯片模块不再是使用传统的C4凸点等方案在基板上进行互联,而是通过一个高信息传递速率的中介层(Interposer)连接。中介层通常是硅基板,内嵌密集的互连通道,可以实现高带宽和低延迟的信号传输。得益于中介层,2.5D封装提供了接近单片设计的性能(带宽高、延迟低),而且支持异构集成(不同工艺、不同功能模块组合),且芯片模块可独立制造,灵活性高。在高端的HPC、AI处理器、GPU等对带宽要求极高的场景,2.5D封装有着非常好的应用。2.5D封装的各个模块的连接还是通过水平的中介层进行的,3D集成则更进一步,将不同的芯片模块堆叠在一起,以垂直方向来进一步增加连接密度。模块之间通过硅通孔(Through-Silicon Via, TSV)或直接铜键合(Cu-Cu Bonding)实现电气连接。不同模块以堆叠形式放置,大幅减少占用面积,且TSV 或 Cu-Cu 键合互联的方式提供了极高的带宽和超低延迟。3D集成芯片占用空间最小,集成密度最高。垂直互连距离短,延迟低,带宽高,异构集成支持不同工艺节点的模块组合。但它的制造和封装工艺最复杂,成本最高,而且散热是3D集成的主要挑战。

整体来看,2.5D 集成技术是目前实际高端应用芯片的主流选择,尤其是在HPC、AI芯片、GPU以及一些高端网络设备中,2.5D 集成占据了非常重要的地位。这主要是因为 2.5D 集成在技术成熟度、成本和性能之间找到了一个很好的平衡点。相比 MCM,中介层的引入使得2.5D集成具有更高的信号传输带宽,以及由信号传输距离变短带来的更低的传输延迟以及更低的功耗,性能有着显著提升。而且相比于3D集成,2.5D集成的散热问题更低,也不需要像3D集成一样精确的TSV和层间对齐技术,工艺更成熟,良率更高。目前2.5D的设计和制造流程已经相对稳定,具有可靠的供应链。比如中介层的材料和工艺已经非常成熟,硅中介层的生产也有大量的代工厂支持(如台积电的 CoWoS 工艺)。2.5D技术在AI和高性能计算领域已经有了大量的应用,比如AMD 的 Radeon Instinct MI200 系列 GPU 使用 2.5D 中介层技术(HBM 高带宽存储和 GPU 核心通过中介层连接)。NVIDIA 的 A100 GPU 使用了类似的技术,支持高带宽内存(HBM)。 Xilinx的高性能AI芯片Virtex 和 Alveo 系列 FPGA 都依赖于 2.5D 技术,通过中介层实现高速互连,等等。整体来看,目前 2.5D 是高性能算力芯片的主流技术选择,也是业界“性能-成本”平衡点上的最佳方案。在 3D 技术进一步解决良率、成本和散热问题之前,2.5D 将会继续主导高性能算力芯片设计。

2.5D集成

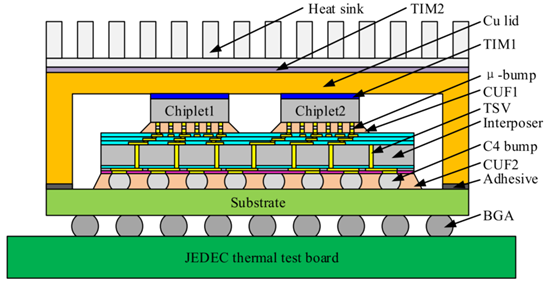

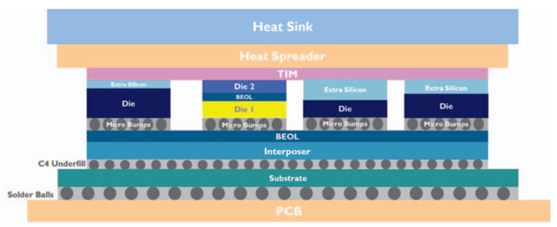

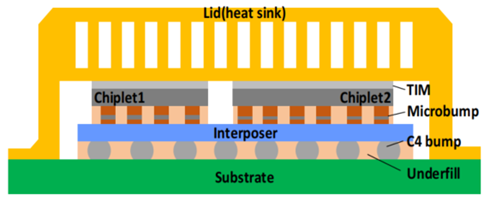

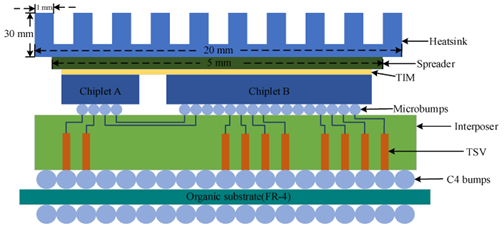

下图展示了一个包含两个Chiplet的基于2.5D封装的芯片结构示意图。两个芯粒通过微凸点(μ-bump)并排安装在中介层上。在芯粒与中介层之间填充了一层毛细填充材料(Capillary Underfill 1, CUF1)。中介层通过C4凸点(C4 bump)与有机基板(Substrate)相连接。在中介层与基板之间填充了另一层毛细填充材料(Capillary Underfill 2, CUF2)。基板BGA焊点组装在JEDEC热测试板上。芯粒的顶部表面以及中介层周边通过TIM1和粘合剂分别连接了一块铜盖板(Lid),通过TIM2在外壳的顶部表面连接一个散热器。

具体到每个Chiplet内部,可能仅包含一个Die,也可能通过3D堆叠技术垂直堆叠多个Die,比如下图所示的结构。每个Die负责特定的功能模块,比如逻辑计算Die(Logic Die)负责主要的计算和逻辑处理任务,通常集成计算单元(如核心、算术逻辑单元 ALU)以及控制单元,使用高性能工艺(如 5nm 或 3nm)提高速度和效率;缓存Die(Cache Die)提供高带宽、低延迟的存储,作为逻辑计算单元的临时数据存储区域。缓存Die使用 SRAM 技术构建,强调高性能和低功耗。其用于缓存高频访问的数据(如 CPU 的 L3 缓存或 AI 加速器的片上缓存),在 AMD 的 3D V-Cache 技术中,缓存 Die 通过 TSV 垂直叠加在逻辑 Die 上;内存Die提供存储数据的能力,支持逻辑Die的计算任务。内存Die使用 DRAM 或 NAND 技术,专注于高存储密度和带宽,在 2.5D封装中,通常通过中介层与逻辑 Die 连接。AI 芯片和 GPU 等高性能计算设备经常使用多个 Memory Die 提供高容量存储。

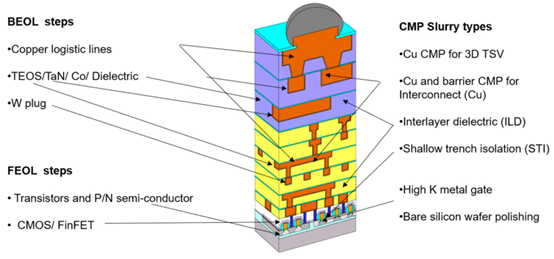

对于每一个Die的内部,根据Die类型的不同其结构会有所区别。但大体上可以分为前道工艺(FEOL, Front-End-of-Line)和后道工艺(BEOL, Back-End-of-Line)两部分,如下图所示。FEOL主要负责构建晶体管及其他基础电路的功能单元,目标是实现基本的开关操作和电路逻辑功能,BEOL主要用于构建金属互连网络,将晶体管和其他功能单元连接起来并提供对外的通电接口,完成信号传输、电源分配等功能。

具体结构

传热路径

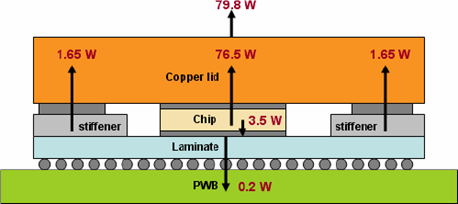

在芯片的实际应用场景中,芯片底部安装在PCB板上,而PCB板侧并没有明确的散热措施,因此向下的传热阻力很大,热量主要从上方以芯片->TIM1->Lid->TIM2->热沉的传热路径散出。因此,TIM2、TIM1、Lid 等外部材料的性能对传热热阻有着显著的影响,而Die下方的结构则影响并不是很大。但对于3D堆叠的情况,多颗Die可能垂直连接在一起,这时候Die间材料及Die内BEOL叠层同样可能会出现在上方的传热路径上。而传统的芯片制造中这些部分的热性能并没有得到足够的重视,预期他们会对芯片的热阻产生大的影响。

外部

TIM

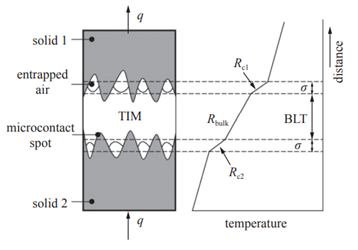

TIM的主要功能是弥补不同材料界面上由于粗糙度导致的气隙,从而提高界面热传导效率。在芯片中,主要有两种TIM,分别是TIM1和TIM2。TIM1位于芯片裸片和盖板之间,主要功能是减少芯片裸片和散热盖之间的热阻。TIM2位于盖板和散热器之间,减少盖板和散热器间的接触热阻。

盖板

盖板是位于芯片裸片上方的散热结构。主要功能是保护芯片裸片免受物理损伤,同时增大芯片散热的表面积,提升热传递效率。芯片的产热大部分都需要经由盖板导出,因此盖板材料对于芯片的热学性能也有着重要的影响。同时,盖板材料的物性也会影响芯片的翘曲,这在Chiplet多热点温度分布不均匀的情况下更加显著。因此盖板材料的热学、力学性能对于芯片封装的可靠性有着重要的影响。

目前最常见的基板材料就是有机材料,比如BT树脂,在消费级产品如CPU、GPU、SoC中广泛应用,具有较低的成本和良好的热稳定性;氮化铝和氧化铝等陶瓷基板导热性强、机械强度高,适用于高功率和高可靠性芯片;硅基板常用于高性能封装(如 2.5D 和 3D 封装),其内嵌硅基中介层,具有良好的信号性能和兼容性。

Die间互联

TSV

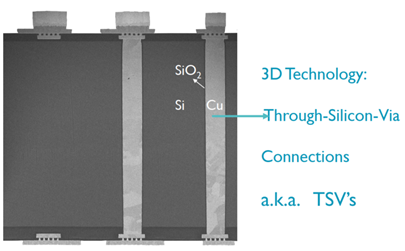

TSV技术广泛用于 3D 封装中,用于实现垂直方向的电气互联。TSV 在硅片中打孔并填充导电材料,形成芯片之间的垂直互联。硅材料通常作为 TSV 的基底材料,支持所有垂直互连。通过硅片的微孔技术,TSV 能够有效地连接不同的芯片层。填充材料用于填充 TSV 通孔的导电区域,实现芯片之间的垂直信号传递。铜是 TSV 填充的主流材料,具有良好的导电性、导热性和稳定性。在某些要求高温或高可靠性的场合,钨因其具有优异的机械强度、耐高温性和低扩散性,也会被用作TSV的填充材料。阻挡层材料沉积在TSV孔内侧壁面,主要用于防止 TSV 填充材料扩散到周围硅区域。常见的阻挡层材料包括氮化钽:热稳定性好,扩散阻挡效果强;氮化钛:适用于早期工艺节点;二氧化硅:电气绝缘性能好,可配合金属阻挡层使用。

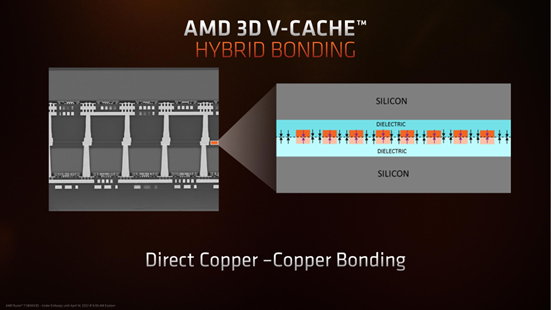

Hybrid Bonding

HB是一种先进的 Die 间互联技术,通过铜-铜键合和介质材料键合,在不同芯片之间提供高带宽、低延迟的电气连接。HB 技术主要应用于 3D 封装、异构集成封装和系统级封装中。HB中主要涉及到了铜和介电材料两种材料。铜-铜键合是实现芯片间电气连接的核心,铜提供了高效的导电性。介电材料的主要作用是电气隔离,避免两层铜之间的短路,确保信号的清晰传输。常用的介电材料有二氧化硅:广泛用于半导体封装中。它具有良好的电气隔离性能,并且能够在高温环境下保持稳定性;氮化硅:具有高介电常数和低介电损耗,在 HB 封装中常作为介电隔离层;聚合物(如 PI(聚酰亚胺)、BCB(苯并环丁烯)等):在 HB 中也被用作介电层,尤其是在多层芯片和高密度封装中。其优势在于柔性和可调性,可以适应不同的封装需求。

Bump

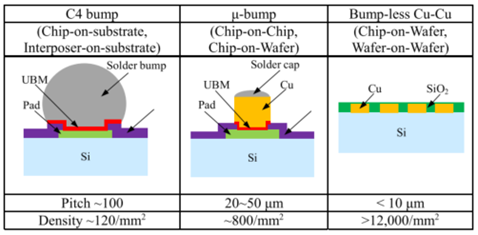

Bump主要用于Die/中介层以及Die/基板之间的电气连接。Bump 技术在芯片中有不同的类型,主要包括微 Bump和C4 Bump。如上一小节所示,相比于Bump方案,直接键合技术中铜表面经过平整化处理(如化学机械抛光,CMP),并通过局部的热压或键合技术(如铜热压键合)实现直接接触。由于没有凸点的尺寸限制,这种方式可以实现更小的间距(<10 μm)和更高的互连密度(>12,000/mm²)。

对于用于芯片和基板间互联的较大尺寸的C4 bump,主要填充材料就是焊料,通常为合金材料。对于Die间的高速互联,比如Die和中介层之间的互联,C4 bump的信号传输速度不能满足需求。因此业界发展了微bump技术。微bump是一种使用铜填充的Bump,可以实现高密度封装和更小尺寸的互联点。微bump的材料主要由铜和焊料两部分组成。铜柱提供了主要的机械强度,能够支持焊接过程中的形变和连接稳定性,铜的高电导率也提供了高频和高速信号传输的支持。焊料负责在铜柱和基板/芯片之间形成电气和机械连接。

Die内

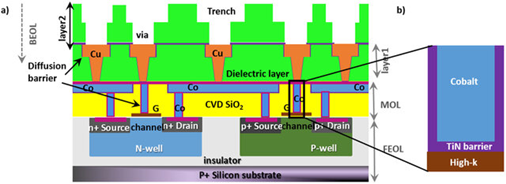

Die是实现芯片具体功能的地方,总的来说Die的制造可以分为FEOL和BEOL两个部分。FEOL 是芯片制造的第一阶段,主要负责构建晶体管及其他基础电路的功能单元,目标是实现基本的开关操作和电路逻辑功能。下图展示了FEOL工艺生成结构的基本示意图,其中MOL(Middle-of-Line)指的是中间工序,将FEOL和BEOL的连接到一起。MOL通常由微小的金属结构组成,作为晶体管的源极、漏极和栅极的触点,这些结构连接到BEOL的局部互连层。

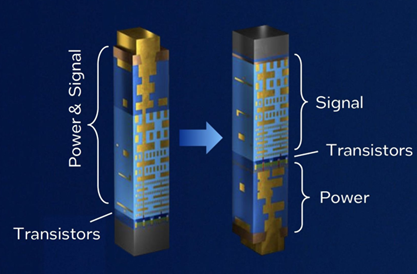

BEOL是芯片制造的第二部分,主要用于构建金属互连网络,将晶体管和其他功能单元连接起来,完成信号传输、电源分配等功能,其基本结构如下图所示。对于更加先进的2nm芯片技术,台积电和三星也在大力发展背面供电网络技术(Back-Side Power Delivery Network,BSPDN),将供电的线路移至晶圆背面,将供电和信号线路分离避免相互干扰,但基本结构和传统的BEOL应该是差不多的。

在BEOL工艺结束后,会进行化学机械抛光(CMP, Chemical Mechanical Polishing),确保各层工艺的平整性。之后,在BEOL的最顶层会沉积一层保护涂层,主要用于保护 BEOL 中的金属互连线和裸片表面免受环境影响。常见的保护涂层材料包括氮化硅、聚酰亚胺(PI,Polyimide)、氮氧化硅(SiON)等。

FEOL

晶体管区域主要由高纯度单晶硅制成,源漏区域会掺杂磷(P)、砷(As)、硼(B)等元素。晶体管的栅极由金属材料和High-k材料构成,用以形成MOS结构,控制电子流动,减少漏电流,提高晶体管性能。其中High-k材料用于形成介电层,提升电容控制能力。常用的High-k材料有氧化铪(HfO₂)、氧化锆(ZrO₂)等。金属栅极需要具有高导电性和低阻抗,常用的材料有氮化钛、氮化钽等。在晶体管和晶体管之间,需要形成浅沟槽(STI, Shallow Trench Isolation)隔离,防止相邻晶体管之间的漏电和信号串扰,填充材料一般是二氧化硅,某些时候也会使用氮化硅作为隔离层。

BEOL

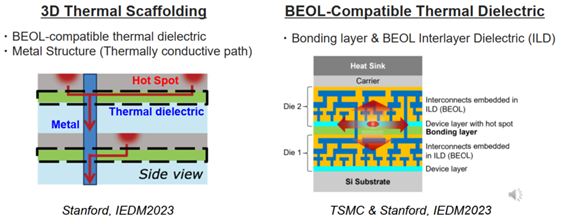

BEOL主要由金属互连线和层间绝缘材料构成。金属互连线一般采用铜,目前业界也在研究新金属材料,其中钌(Ru)被认为是最有前景的一种金属材料之一。金属互连线的周围用层间Low-k介电材料填充,用于隔离各金属层,防止信号干扰同时减少寄生电容。在互连线和介电材料之间,会生长氮化钽、氮化钛等阻挡层,防止金属扩散到介电层中。常见的绝缘材料有二氧化硅:传统材料,热稳定性好;Low-k材料:如碳氢化合物(SiLK),适用于先进工艺节点;氮化硅:在某些场景下用作机械增强层。绝缘材料一般热导率较低,往往会对传热有着非常大的阻碍。同时随着先进制程的发展,在背面供电网络下BEOL对晶体管层的发热会有着更大的阻碍,因为此时器件层上下两侧都被BEOL包围了。因此近年来,国际上很多领先的企业和科研院所都在关注BEOL的散热问题,如Stanford、TSMC等。