GaN器件近结热管理及建模简化的影响

GaN器件近结热管理及建模简化的影响

简介

Kim T, Song C, Park S I, et al. Modeling and analyzing near-junction thermal transport in high-heat-flux GaN devices heterogeneously integrated with diamond[J]. International Communications in Heat and Mass Transfer, 2023, 143: 106682.

今年发表在ICHMT上的Jungwan Cho实验室的一篇文章,分析了各种建模简化对器件仿真结温的影响,讨论了器件有限元热仿真中经常采取的几个简化。Cho实验室这个方向文章的特点是量大管饱,每次都介绍一大堆参数设置和物性计算的模型,给出一系列参数化分析的曲线和结果,看这些结果想一想规律有时候会蛮有启发的。但他们的Discussion一般没什么意思,完全是对数值结果的陈述,同样的结构也经常编个新故事给出另一个侧面的新结论,不过不同故事的思路还是蛮清晰的,用来训练写作是很好的素材.. 有些文章的Discussion每次读都有新的体会,感觉自己当初的认识还是太浅,实践了更多之后才能感受到作者为什么要写这句话..

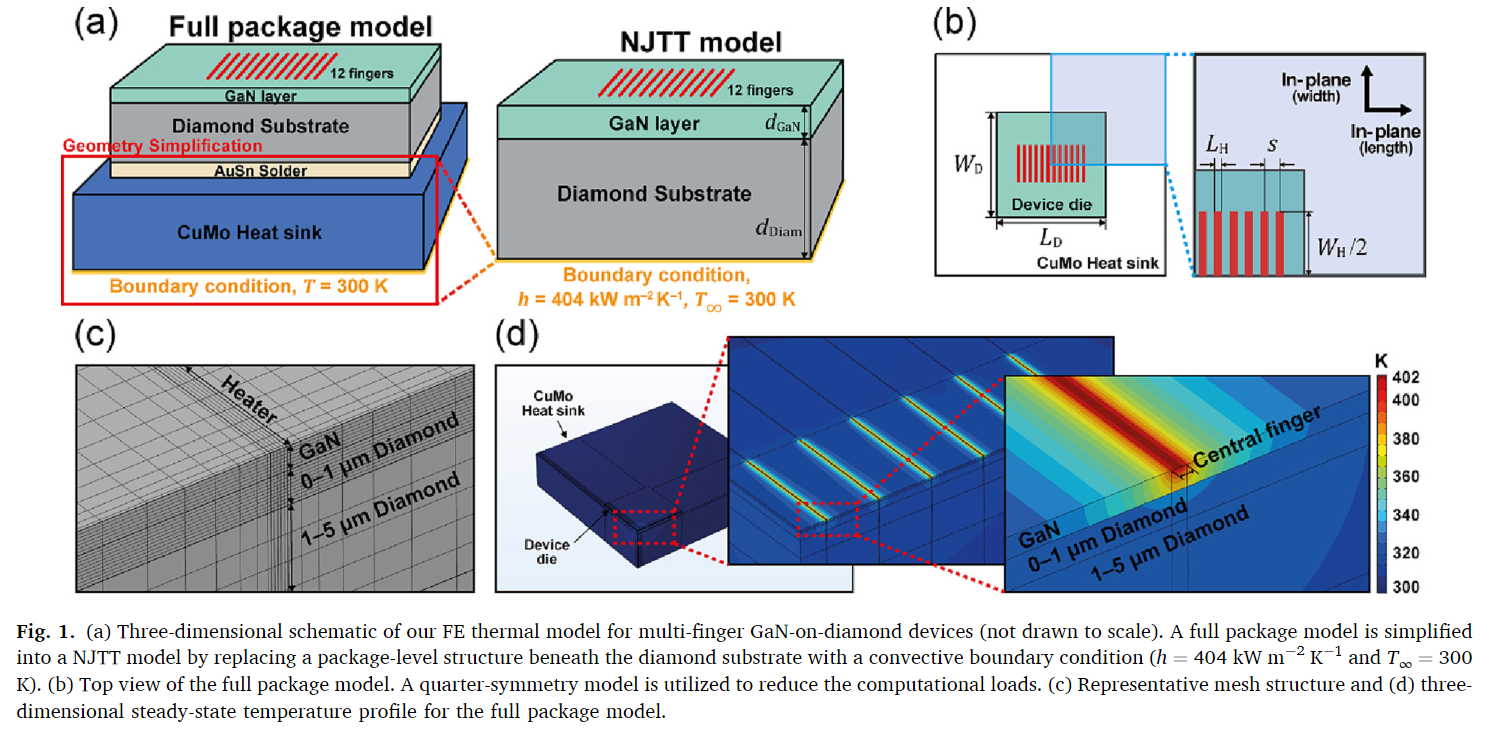

他们这个文章讨论了三种器件热仿真的建模简化,

- package simplification:忽略掉衬底下方的封装结构

- dimension simplification:从三维简化到二维,只仿真长度方向的一个截面

- detailed transistor structure simplification:忽略掉GaN层上方的复杂结构,比如缓冲层、钝化层、金属电极

在温度场预测上,这篇文章主要有三个结论,

- 忽略下面的封装结构是可以的,只要选一个合适的对流换热系数

- 三位简化到二维的结温可能被高估30%

- GaN层上方的结构对结温没什么影响

然后基于得到的这三个结论,用简化的模型去分析了几个参数对结温的影响。关于温度预测上这三个结论应该是没什么问题的,不过这些分析总感觉错过了些重要的问题,这点Kevin R. Bagnall、Yuri S. Muzychka和Evelyn N. Wang之前的讨论明显就更深入一些。有些细节和推论还值得再仔细推敲一下,因为在近结热管理改进器件设计参数上,预测结温的确重要,但是更重要的是预测热阻随结构参数的变化趋势,这里有些令人困惑的是,一旦简化选取的不合理,得到的热设计趋势完全是相反的,并不简单地是温度预测准确与否的问题。这个Blog首先梳理一下HEMT器件的仿真结构,然后讨论一下近结热输运过程的主要特点,根据这些特点,分析一下忽略封装结构和单周期简化对热设计趋势变化的影响。

器件近结热输运

示意图

下面这个是一个经典的GaN器件的结构示意图,GaN层+衬底构成所谓的近结区域,我们把这一块称作Die,Die的长度和宽度都在一千到几千个微米左右的量级内。热量在GaN层顶部的二维电子气处产生,对于多栅器件,热源可以建模为在GaN层顶部的多个周期性排布的热流边界,栅之间的距离,也就是热源之间的距离,我们称之为pinch distance。我们需要把近结区域贴到外层封装结构上,中间我们一般采用金锡焊料来把两部分粘起来。在不考虑一系列过渡层以及GaN层顶部复杂结构的情况下,实际上大家分析的GaN器件就是贴到一起的四层方块。

在有限元热仿真中,我们可以改变哪些几何参数来减小器件的热阻呢?竖向主要是各层的厚度,沿长度方向主要是栅间距(一个栅对应一个热源,但是不能把热源的长度当作栅长,继而去分析栅长对器件热阻的影响,改进器件栅长的设计,这个分析是完全错误的,可以参考之前写过的栅极热流假设)。在改这些参数的过程中,很多其他的参数会影响结果,包括界面热阻、热源长度和宽度这些,因此在各种文章里,一般会分析不同组其他参数下可设计的几何参数的变化。

近结热管理

(这里不讨论嵌入式冷却、倒装封装这些问题,只讨论各层的几何及热物性参数对器件热阻的影响)近结热管理的艺术,在于扩展热阻和一维热阻之间的平衡。首先想象一个一维导热问题,热量从一侧出发,经过很多层及他们之间的界面后,流向另一侧。这个过程的热阻非常直接,哪一层越厚,热导率越低,哪一层的热阻就越高,各部分的热阻完全是解耦的,比如把某一层减薄这层的热阻就减小了,对其他部分没有任何影响,器件的总热阻也就相应减小了。而近结热输运中,有可能某一层越厚,反而器件的总热阻越小,为什么会这样呢?唯一的区别就是导热不再是一维过程了。

(Journal of Thermophysics and Heat Transfer, 2016, 30(4): 863-879.)

热量从一个小的热源出发,扩展到更大的区域,越靠近热源,热扩展的效应越强,靠近小热源区域的热设计规则完全由扩展热阻所控制,此时采取措施增强热扩展能力把热量铺开,可以有效地促进热量输运降低器件热阻。而随着热量向下输运,热扩展效应逐渐减弱,一维导热过程的占比又逐渐增加。而当远离热源的时候,热扩展效应基本消失,传热过程又由一维热阻所控制。

所以对于一个器件的近结热设计,各个参数往往会存在一个最佳设计点,比如下面是Cho这篇文章里所展示的不同TBR下增加GaN层厚度器件结温的变化。整体来看,随着GaN层厚度的增加,器件结温先大幅降低,达到一个极值点后,缓慢增加。出现这个趋势是因为,当GaN层较薄时,热量在GaN层还有大幅的扩展空间,此时增大GaN层厚度,可以有效地降低扩展热阻。而达到某一个极值点后,GaN中的热扩展能力基本达到极限了,继续增大GaN层厚度,扩展热阻也不会怎么降低了,反而会导致一维热阻的增加。而虽然扩展热阻不再降低了,但是其绝对值还是远大于一维热阻,所以此时结温随着GaN层厚度的增加只有略微地上升。GaN和衬底间TBR的值越高,这个极值点对应的GaN薄膜越厚,这引出了近结热输运过程的另一个特点,各部分热阻对热输运的影响是高度耦合的。根据TBR的定义,局域温度跳跃和局域热流成正比,它相当于起到了一个滤波器的作用,当TBR很高时,热流经过界面后的不均匀性被大幅削弱,即使此时衬底的热导率很高比如金刚石衬底,热量在衬底中也不再有足够的扩展空间。此时增强热扩展能力,只能着手于界面之前,也就是GaN缓冲层。即使缓冲层的热导率低于衬底,但是增加缓冲层厚度,可以有效地减缓界面处热流的不均匀性,使得界面热阻的阻碍作用减小,降低器件整体热阻。

建模简化的影响

忽略封装结构

Kevin R. Bagnall等分析了忽略下层封装结构和不同边界条件对GaN-on-金刚石器件热阻的影响,他们发现当考虑下层封装结构时,器件热阻随着金刚石衬底厚度的增加而减小,而当去除下层结构并将衬底底部设置为等温边界时,观察到完全相反的趋势,总热阻随着衬底厚度的减小而降低。出现这种结果是因为热量在衬底中的输运仍然是高度不均匀的,当考虑封装结构或者将衬底底部设置为对流换热边界条件时,在总功率一定的情况下,热流分布越不均匀,则下方封装结构所占的热阻比例或者对流换热边界界面处的温度跳跃就越大,这导致了更大的器件总热阻。而在此时增大金刚石衬底厚度,可以让经过这个界面的热流更加均匀地铺开,在总功率一定的情况下,则降低了经过界面的最大温度跳跃,从而降低了器件总热阻。而如果将衬底底部设置为等温边界,则这个效应就完全没有体现出来,因为温度到最下面被人为束缚成均匀的了。对于具有薄 (~50 μm) 金刚石衬底的大型 GaN PA,衬底下方边界的等温是基本不可能实现的。 因此,使用等温边界以及忽略芯片封装结构会导致与衬底厚度有关的错误趋势。

(IEEE Transactions on Components, Packaging and Manufacturing Technology, 2014, 4(5): 817-830.)

当增大金刚石衬底厚度的时候,虽然金刚石衬底中所占的热阻比例上升了,而封装结构中的热阻比例却下降了,最终总热阻下降了,这个原因可以从两点来进行分析。首先,假设忽略封装结构,把衬底底部设置成一个对流换热边界条件,那么流过这个界面的热流越均匀,则最高温度跳跃就越小,总热阻就越小。另一方面,右边Cho文章中的这个图给出了忽略封装结构时,衬底底部的等效对流换热系数随衬底厚度的变化。可以看到这个等效对流换热系数也是随着衬底厚度的增加而降低的,这说明当热流变得均匀的时候,下层封装中的扩展热阻也减小了。

单周期近似

单周期简化可以近似地反映多个热源的影响,比如Multifinger器件有多个热源,每一个热源的发热都会提升旁边热源的温度,我们把这种现象叫作热串扰(Thermal crosstalk),

Thermal crosstalk(热串扰)是指在电子设备或集成电路中,由于热量的传导和散热路径之间的物理接触或靠近而导致的热相互影响现象。当不同热源之间存在热传导路径或热散热路径时,它们之间的温度变化可能会相互影响,进而引起热量的传递或温度的变化。

热串扰可能会对设备的性能和可靠性产生不利影响。当一个热源产生高温时,周围的其他部分可能会受到热传导而升温,进而影响它们的正常运行温度。这种热相互影响可能导致设备的热不平衡、温度梯度过大、工作温度超出设计规范范围等问题。

为了减小热串扰的影响,设计者可以采取一些措施,例如优化散热路径、改善热传导接触、调整元件的布局等。通过合理的热管理设计,可以降低热串扰的影响,提高设备的热性能和可靠性。

总而言之,热串扰是指在电子设备中由于热量的传导和散热路径之间的物理接触或靠近而导致的热相互影响现象。它需要在设计和优化过程中加以考虑和控制,以确保设备的热管理达到预期的要求。

一些理论研究,或者在TCAD电热耦合仿真中近似考虑热串扰的影响,可以只研究一个单周期,不会改变整体得到的结论,比如对声子弹道传热的一些分析,

(IEEE Transactions on Electron Devices, 2019, 66(8): 3296-3301;IEEE Transactions on Electron Devices, 2022, 69(6): 3047-3054;IEEE Transactions on Electron Devices, 2023, 70(2): 409-417;International Journal of Heat and Mass Transfer, 2023, 211: 124284)

在TCAD仿真中考虑thermal crosstalk对电学性能的影响。

(IEEE Transactions on Electron Devices, 2013, 60(7), 2224-2230)

然而在器件总热阻分析中,这种简化会引起完全错误的优化趋势。实际多栅器件,如下图所示,栅一般位于Die的中央,周围有着很多空白的区域。这个时候,周围这些没有热源的区域大幅增加了热量可以扩展的区间范围,导致扩展热阻占总热阻的比例大幅增加。之前提到过,近结热设计方向的关键就是扩展热阻和一维热阻之间的平衡,如果低估了扩展热阻的比例,这会导致完全不同的优化结果。比如现实中金刚石衬底越厚,器件总热阻越低,因为这增强了热扩展;而一旦只考虑一个周期,忽略了周围这些无热源的扩展区域,就会得到金刚石衬底越厚,器件总热阻越高的结论。

(IEEE Transactions on Components, Packaging and Manufacturing Technology, 2014, 4(5): 817-830.)

在Comsol里做了一个非常简单的两层结构,上方是1微米的GaN,热导率设置为\(120 \,\mathrm{W/mK}\),下方是金刚石衬底,热导率设置为\(1800\, \mathrm{W/mK}\),底部对流换热系数设置为\(4\times 10^5\, \mathrm{W/m^2K}\),TBR设置为\(5 \, \mathrm{m^2K/GW}\),上方排列有7个\(200\,\mathrm{nm}\)的热流边界。每个热源之间的距离设置为100微米。如果完全按照周期性结构排列,那么左右两侧热源距离边界的距离应该是50微米,结构的总长度为700微米。这里稍微放大了一点,将结构总长度设置为1000微米,左右两侧距边界的距离为200微米。

即使这样并不算很大的差异,也足以使得结构最高温度随着衬底厚度的变化趋势发生逆转了。然而整体上温度出于同一水平范围内,所以这种单周期近似可以近似考虑thermal crosstalk对结温的影响(相比于single finger的提高),但是不能用来做器件的设计和结构优化。