MOSFET(2)-基本应用

MOSFET(2)-基本应用

Gallium nitride (GaN) high-electron-mobility transistors (HEMTs) are essential and important devices for high-frequency power amplifier and switching applications......

【公开课】普渡大学 - 晶体管基础(双字,Fundamentals of Transistors,PurdueX)

引言

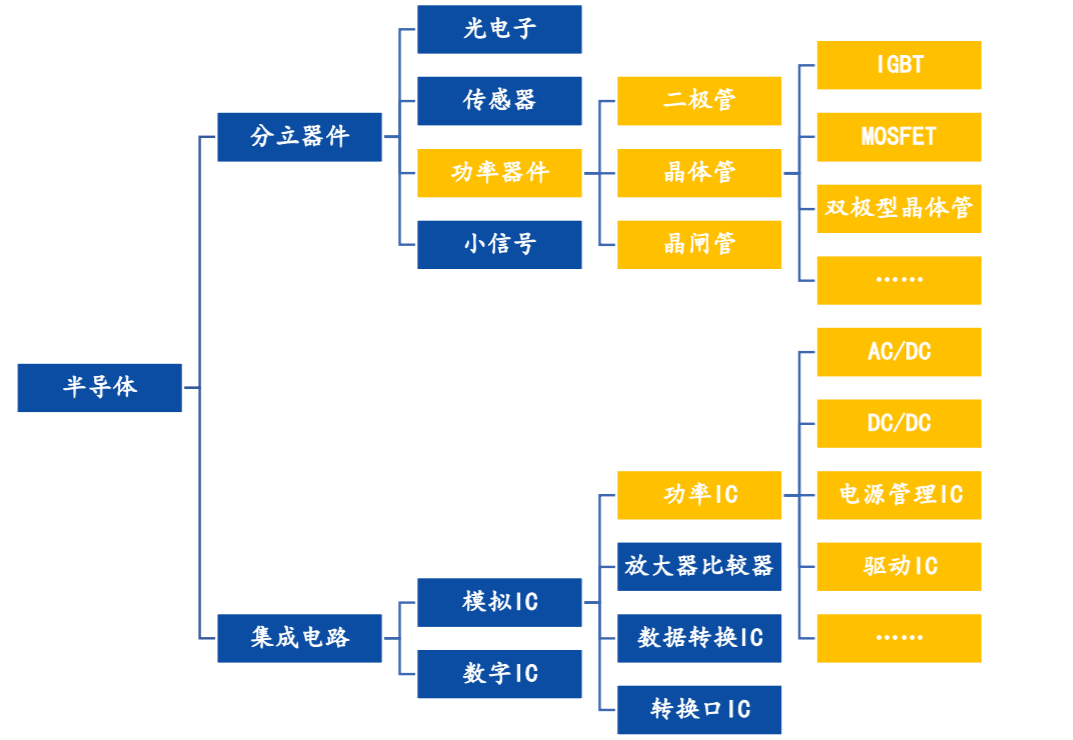

半导体产品大致可以分为分立器件和集成电路 (Integrated circuits, IC)两类,集成电路就是把各种基本的电路元件小型化后连接构成电路,制作在一个小型晶片上,最后统一封装起来后形成具有一定功能的单元,集成电路的优势是在较小的体系内实现了尽可能多的功能. 分立器件就是不进行集成,把某一个元件单独拿出来封装使用,因为它只需要考虑自身的性能,少了许多限制,因此在某一个特性上可能会远好于集成电路。在性能要求比较特殊的情况下,比如超大功率场合,分立器件占据不可替代的地位.

以功率半导体为例,它可以分为功率器件和功率IC,功率分立器件就是将二极管、晶体管或者晶闸管单独封装好构成的单一器件,而功率IC则是将晶体管、电阻、电容等原件集成在一个晶片上封装好构成的电路结构。晶体管中最常见的就是MOSFET,金属-氧化物半导体场效应管,一个用电压控制沟道中电流通断的小型开关. 把单个MOSFET封装起来就是分立器件,按照设计版图采用无数次光刻刻蚀出无数个连接在一起构成逻辑电路的MOSFET大概就是IC (maybe).. 平时实验或热电仿真所处理的对象应该都是未封装的分立器件.

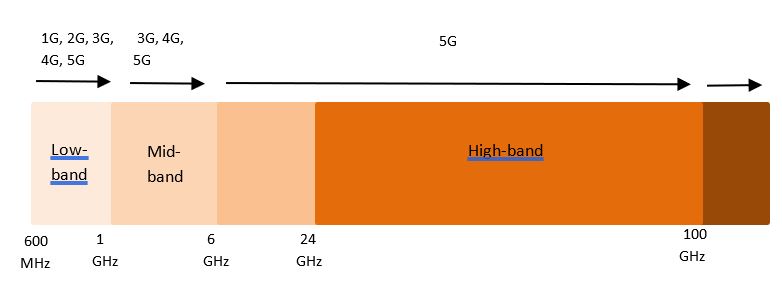

HEMT也算是一种场效应管 (FET),它也是利用在Gate上施加电压产生的电场来控制源极和漏极之间的电流通断. HEMT主要应用于微波和无线电场合,大多数手机、WiFi和类似系统的无线电接收器使用HEMT进行无线电的模拟信号放大,也就是所谓的射频 (Radio Frequency, RF)应用。3G -> 4G -> 5G的通信频段越来越高,也就需要半导体能够在更高频段工作,所以之所以GaN在5G中有着很好的应用前景,也是因为由它构成的射频器件有着更高的极限工作频率.

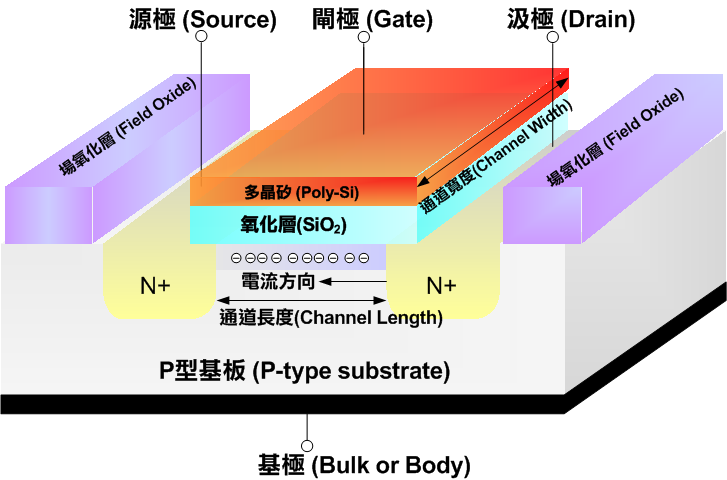

HEMT与MOSFET形成导电沟道的原理是不同的,对于MOSFET,中间Gate是由氧化层构成的MOS电容,左右两侧是重掺杂的源极和漏极. 源极和漏极的中间区域用一个极性相反的区域隔开,也就是所谓的基极区域. 对于NMOS (即源极和漏极区域为N型掺杂的MOS)而言,真正作为导电沟道让载流子通过的只有Gate正下方半导体的表面区域. 当正电压施加在Gate上,带负电的电子就会被吸引到表面,形成导电沟道,让N型半导体的多数载流子——电子可以从源极流向漏极. 因此MOSFET的Gate电压实际上是控制下方导电沟道的形成.

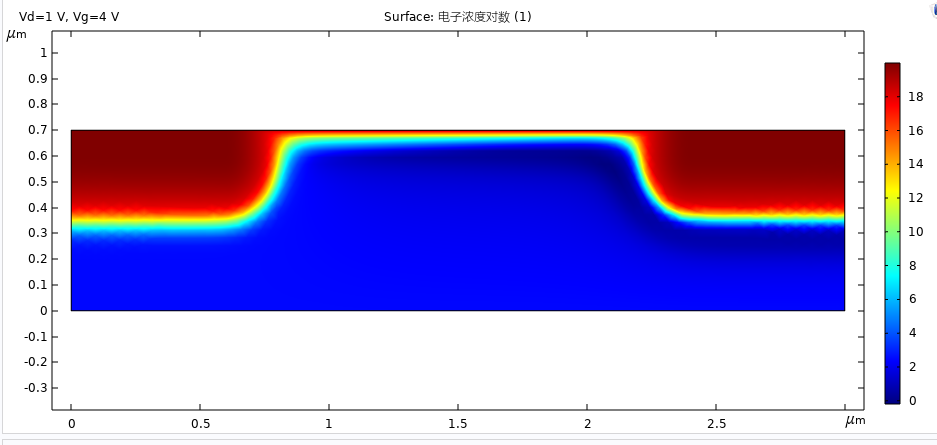

下面是一个简化的的N-MOSFET工作时的电子浓度分布,可以看到左右两侧的源极和漏极都是高N型掺杂区域,在Gate上施加了正电压后,Gate正下方形成了一层高电子浓度的导电沟道,让电子可以从源极流向漏极,此时MOS管打开.

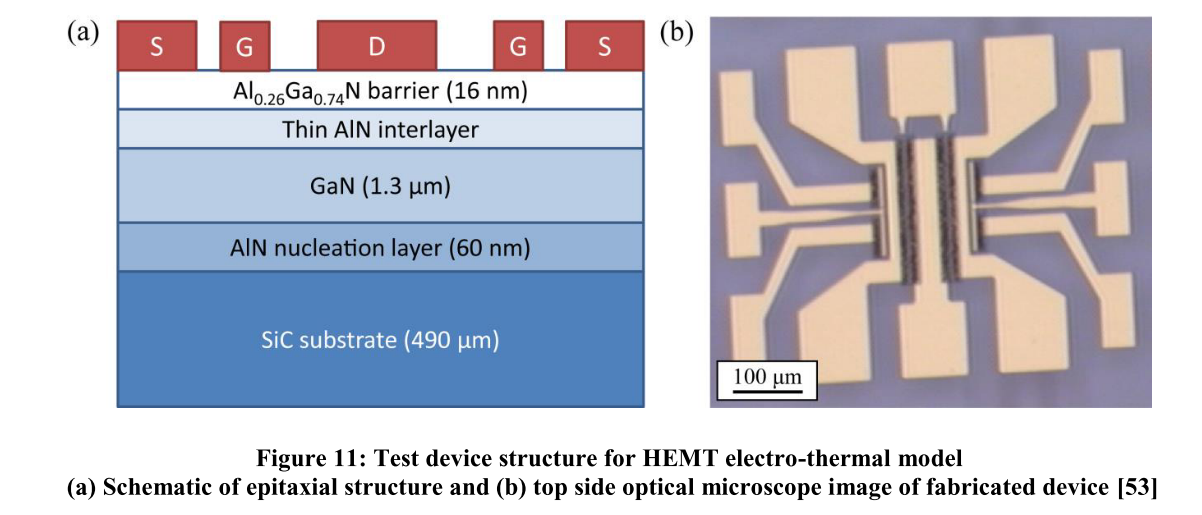

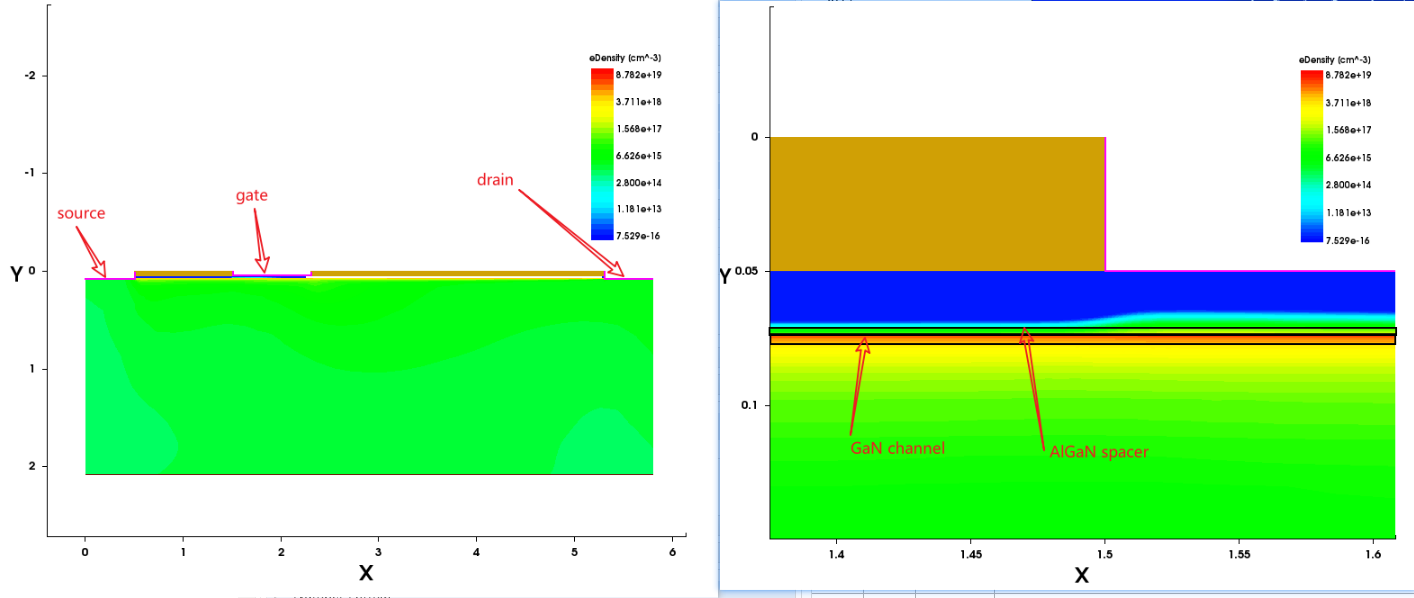

HEMT使用两种具有不同能隙的材料形成异质结为载流子提供沟道. 在GaN HEMT中,GaN channel层和AlGaN spacer层之间形成了一层二维电子气 (2DEG),HEMT实际上是靠这一层2DEG导电的,并不是像MOSFET一样在Gate下方表面形成了一层导电沟道让源极和漏极的重掺杂区域的载流子可以导通. HEMT通过调节Gate电压,可以调控沟道中的2DEG密度,进而实现对开关的控制. (具体什么原理只能来日方长了)

下面这个仿真source、gate、drain中间的部分是绝缘层,把这三个东西隔开. 结果显示电子密度高的地方只有GaN channel和AlGaN spacer之间界面处薄薄的一层.

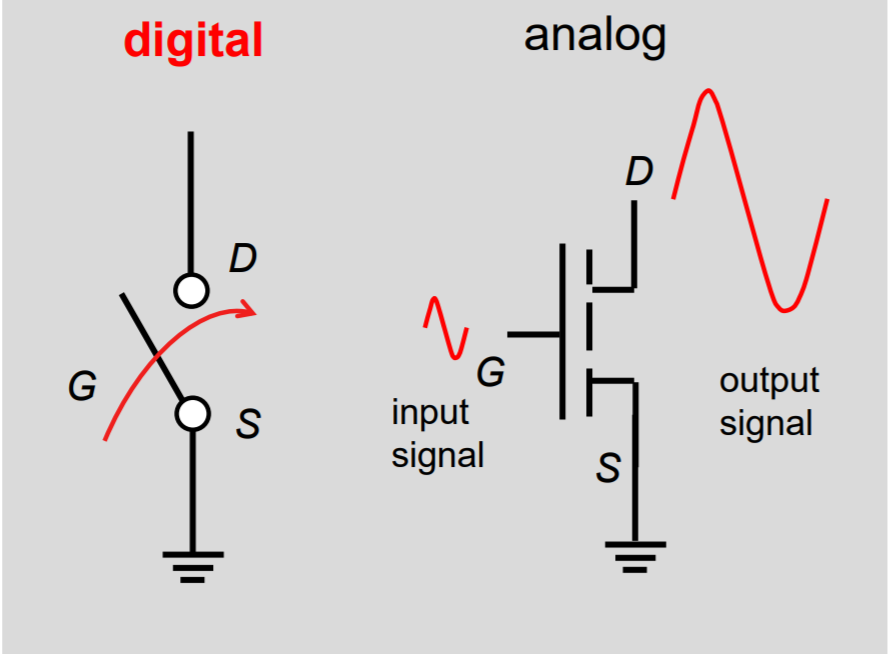

MOSFET的应用分为数字和模拟两大类. 在数字电路中,MOSFET起到类似于开关的作用,输出0、1信号,应用最广泛的MOSFET数字电路之一就是低功耗的CMOS电路,下面主要讨论的也就是这个电路的一些特点;模拟应用是对各种频率的连续的模拟信号进行处理,比如对输入信号进行变换或者放大等操作. 射频 (Radio Frequency)应用大概是模拟应用的一种,大概指用于处理信号处于无线电频率 (射频)的电路 (maybe),主要用于无线通信系统.

Digital Circuits

单个晶体管

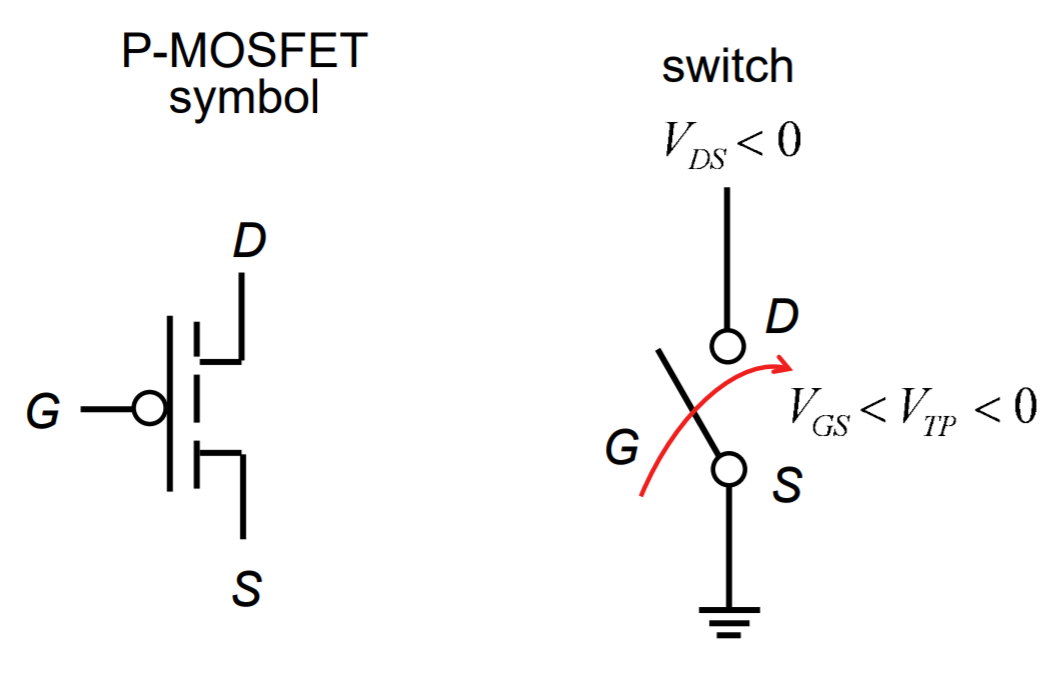

以一个常闭型的晶体管为例,正常情况下它是关着的,Drain与Source之间没有电流. 当对Gate施加电压到阈值电压时,Drain与Source之间导通. 通过对Gate上电压的控制,就实现了电路开关的功能.

CMOS反相器

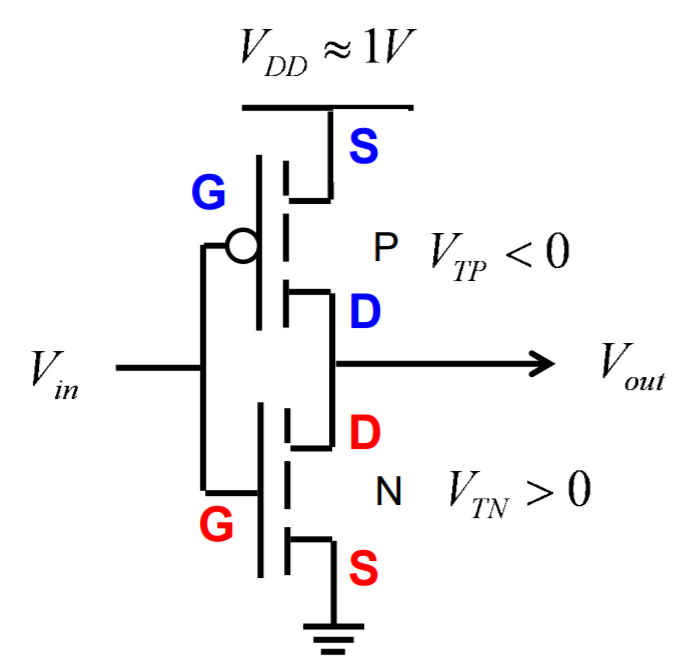

反相器是在数字电路中实现逻辑非功能的逻辑门,可以用一个P型晶体管和一个N型晶体管来实现这个功能. 因为P和N是互补的,因此我们将它称之为CMOS (Complementary MOS)反相器.

把一个P型晶体管和一个N型晶体管接到一起,下方N型晶体管的Source接地 (低电平),上方P型晶体管的Source接在高电平上,两个晶体管的Gate连在一起,Drain连接到输出.

P型晶体管的是空穴导电,因此只有当Gate的电压负到低于阈值电压时,Source与Drain才会导通;N型晶体管是电子导电,因此只有当Gate的电压正到高于阈值电压时,Source与Drain才会导通.

假如现在向Gate端施加一个高电平,此时下方N型晶体管Drain-Source导通,上方P型晶体管关闭,输出端和下方的低电平构成通路,输出低电平;如果向Gate端施加一个低电平,上方导通,下方关闭,输出端和上方的高电平构成通路,输出高电平. 于是实现了逻辑非功能.

CMOS反相器的优点是在理想情况下,除了在01切换的时刻,电路中是没有电流存在的,因此COMS反相器的功耗非常小. 在实际的集成电路中,这两个晶体管都不会处于完全开路状态,沟道中还是会有一定的载流子流动,因此会有微小的漏电电流 (Leakage Current).

CMOS的响应速度和功耗

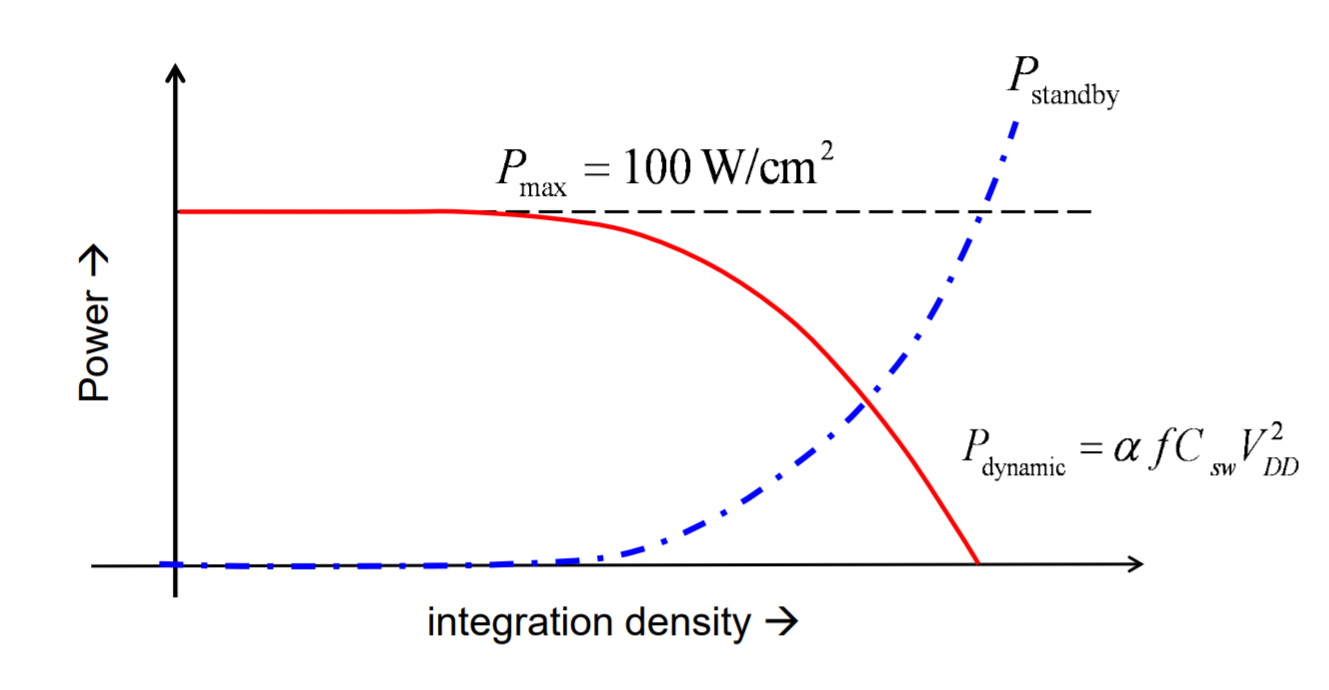

可以把CMOS反相器的输出端看成是连接了一个电容,它的响应速度就是这个电容充放电的速度,因此CMOS反相器的响应速度取决于电路导通时的直流电流大小,更高的DC电流意为着更快的响应速度. \[ \tau = \frac{CV_{\text{DD}}}{I_{\text{on}}} \] CMOS中存在两种功耗,一种是在开关切换时等效于电容放电产生的动态功耗\(P_{\text{dynamic}}\),一种时因为泄漏电流产生的静态功耗\(P_{\text{static}}\). 对于\(P_{\text{dynamic}}\),其表达式为 \[ P_{\text{dynamic}} = \alpha \frac{1/2 \cdot CV^2}{1/2\cdot T} = \alpha fCV^2 \] 其中\(\alpha\)为活性因子,因为不一定每个周期CMOS都会工作,\(\alpha<1\). 开关频率越大,动态功率就越大,也就产生了更大的能量耗散,电路也就越热. 对于\(P_{\text{static}}\),其表达式为 \[ P_{\text{static}} = N_{\text{G}} I_{\text{off}} V_{\text{DD}} \] \(N_{\text{DD}}\)为门的数量,无论是动态功耗还是静态功耗,都随着电压的增长而增长.

由于热问题,电路在设计时一般都有一个允许功率上限,我们称这种为Power constrained design.

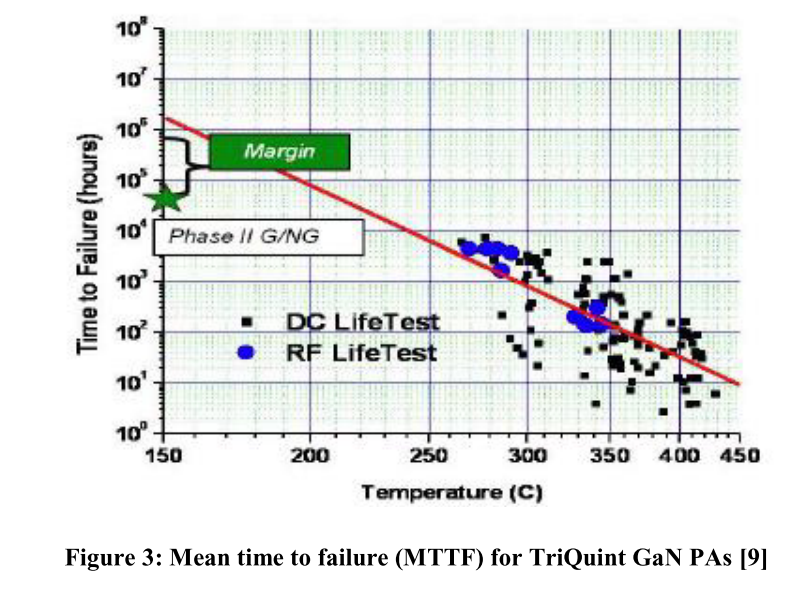

在电路集成度较低时,动态功耗占了绝大部分,随着集成度的提高,漏电导致的静态功耗逐渐上升. 在设计时需要使得动态功耗和静态功耗之和小于许用功率上限. 实际上在电子器件热管理的设计中很多时候是Temperature constrained design,一方面器件的寿命随着温度的升高而指数下降,且随温度增强的电子散射会显著降低迁移率,抑制输出电流;另一方面当温度超过某个值时,也可能会对器件造成不可逆的损坏,(A perspective on the electro-thermal co-design of ultra-wide bandgap lateral devices, Device-level thermal analysis of GaN-based electronics). 因此很多热管理的文章在讨论设计方案和工作区间时,会着重强调能够使得器件温度小于某个临界值(比如200℃)的参数组合,或者按照这种Temperature constrained design来组织文章和讨论的思路 (Thermal management strategies for gallium oxide vertical trench-fin MOSFETs, Modeling and analysis for thermal management in gallium oxide field-effect transistors).

Analog and RF Circuits

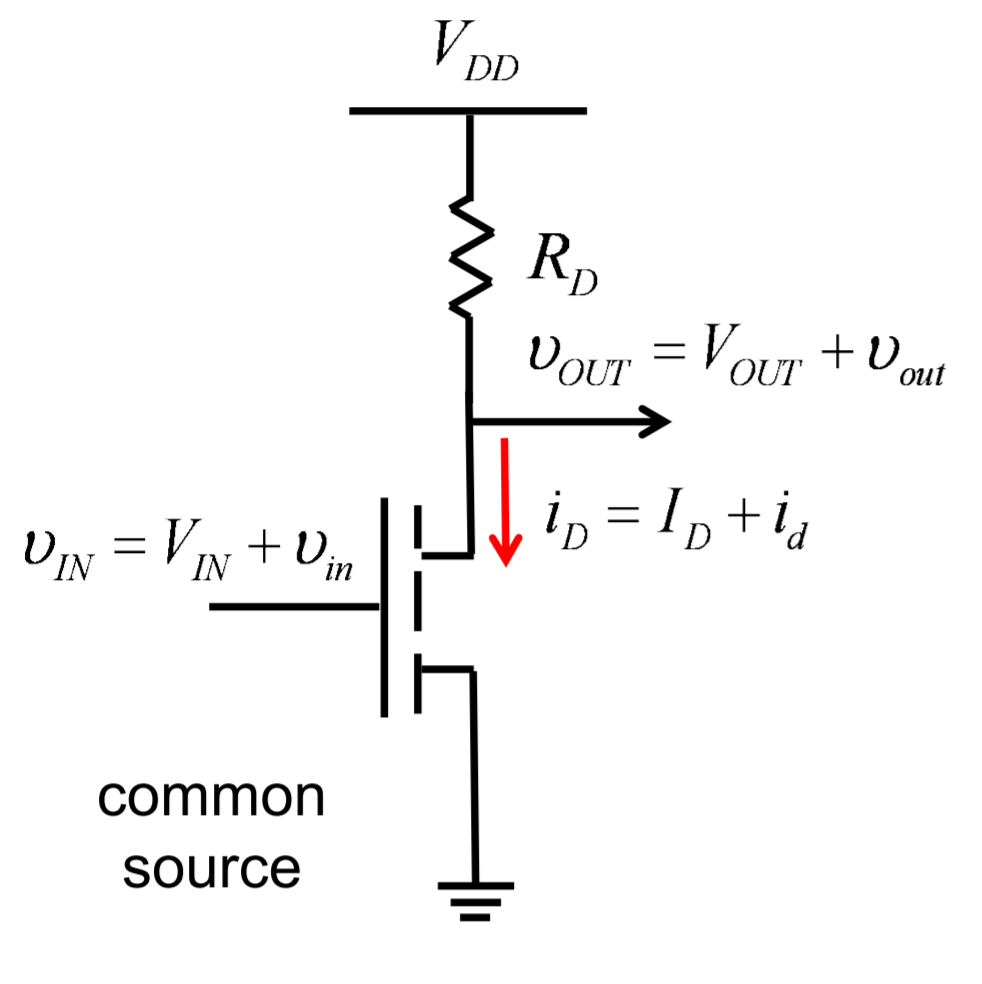

一个MOSFET就可以作为一个放大器. 一个N型晶体管,同样是栅极连接到输入电压,漏极连接到输出端,和高电平相连. 输入电压由较大的直流部分和较小的交流部分组成,输出也是对应的较大的直流信号和较小的交流信号.

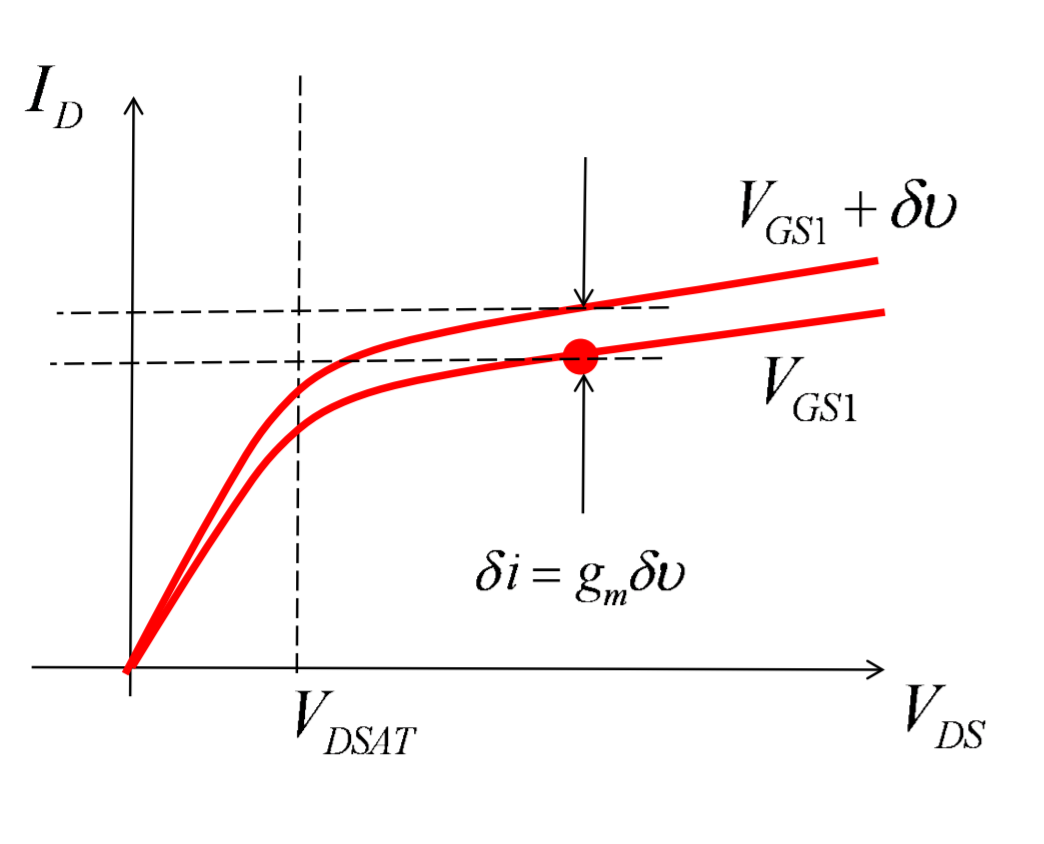

DC直流部分的输入和输出关系已经由MOSFET的电流电压特性给出了, \[ I_D = f(v_{GS}, v_{DS}) \] 交流部分很小,可以认为输出和输入呈线性关系,线性系数\(g_m\)称为跨导 (Transconductance), \[ i_d = g_m v_{gs} \] 而又是由于交流部分很小,因此\(g_m\)又可以近似成 \[ g_{m}=\frac{i_{d}}{v_{g s}}=\left.\frac{\delta I_{D}}{\delta V_{G S}} \approx \frac{\partial I_{D}}{\partial V_{G S}}\right|_{V_{D S}} \] 线性近似下的玻尔兹曼方程也是这么推出来的,也是将分布函数分为较大的平衡分布函数和较小的非平衡部分,将分布函数的梯度用平衡分布函数的梯度近似,书楠师兄告诉我这就如果这个关系不成立就叫作非局域 (non-local),这个精神还要再领会一下.. 自然界的大部分现象在小扰动下都是近似呈线性的,而平衡点附近的势能一阶导数为0,因此势能的表达式基本都是简谐的,简单的泰勒公式给出了很多很直观的图像.

跨导与最大电压放大倍数

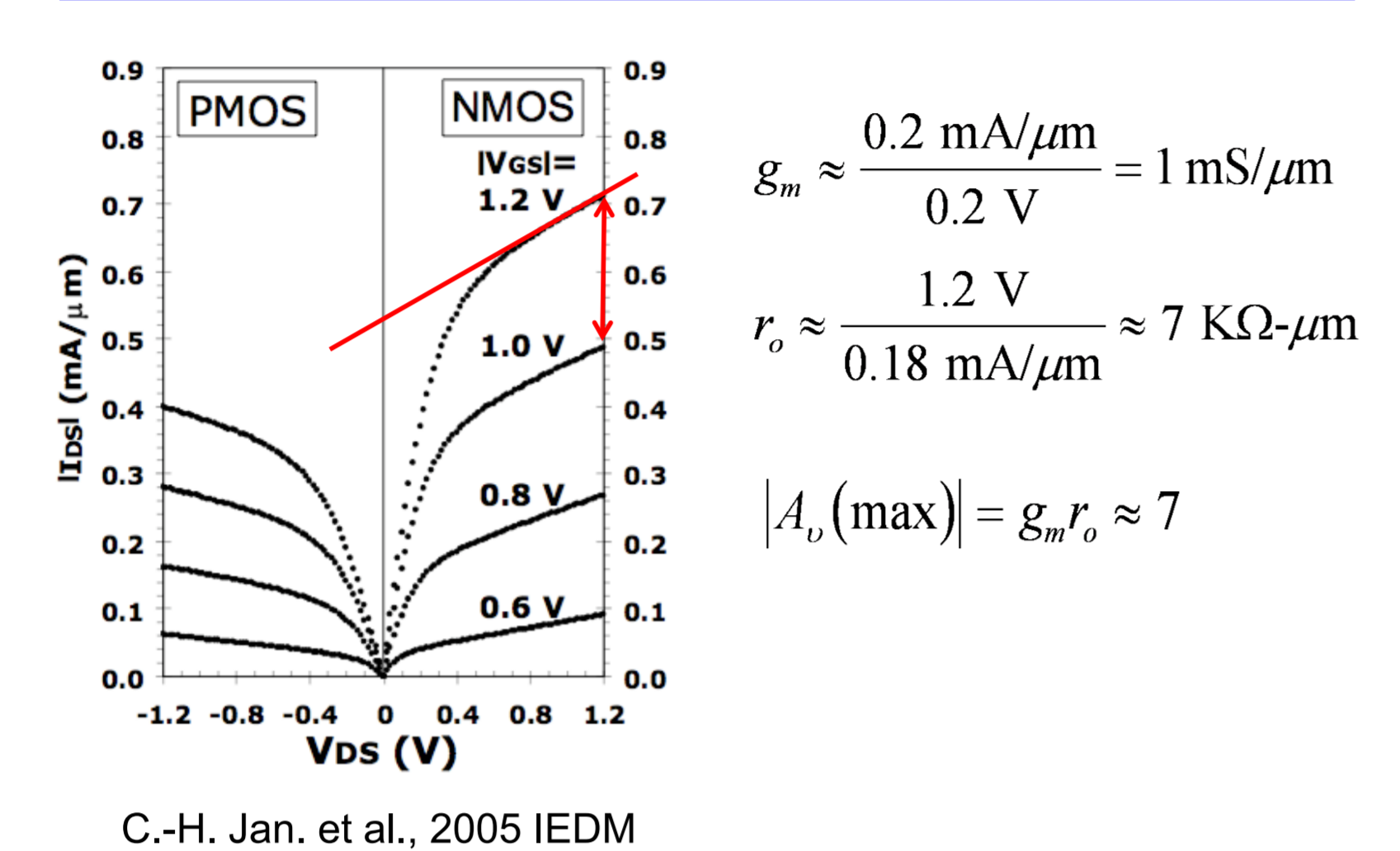

从晶体管的输出特性曲线上可以分别得到跨导和晶体管的等效电阻:

跨导\(g_m\)的值就是输出电流的增加量与栅极电压的增加量之比.

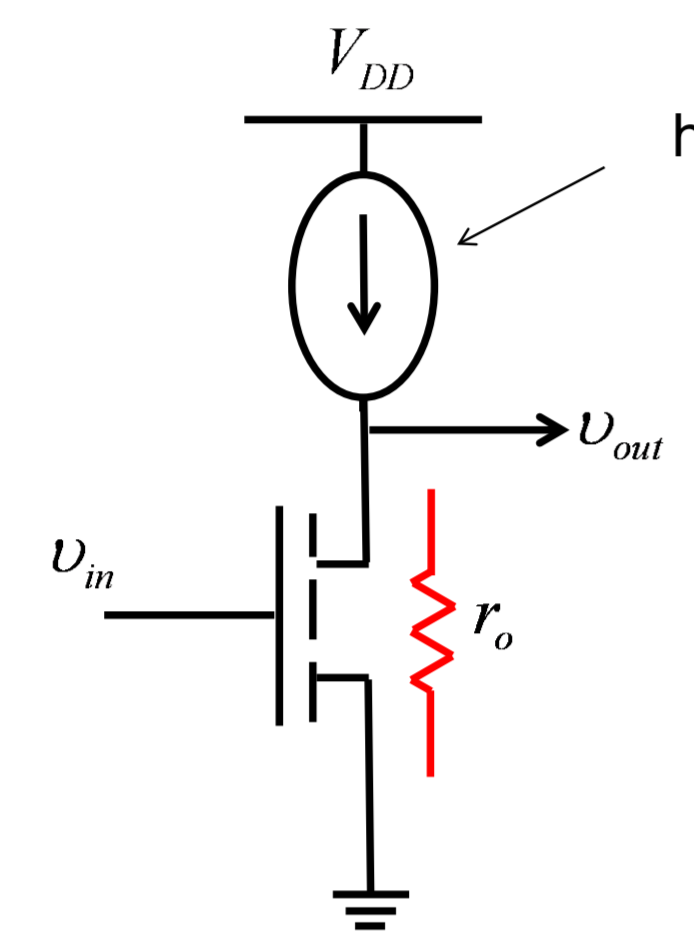

而在饱和区,晶体管的电流电压特性体现出电阻的特点,将这个等效电阻记作\(r_0\),如下图所示.

因此就可以得到理论最大电压放大倍数了,从输出电压的回路来看,实际上相当于上下两条支路的并联,因此在输出电流确定的情况下,各个支路上的电阻越大,电压放大倍数也就越大. 实际的工艺允许把上面支路做成近似电流源,即电阻可以做到接近无穷大,等效电阻就相当于下方支路的电阻,因此最大电压放大倍数为 \[

A_v(\max) = -g_m r_0

\]

从上面的分析可以看到,只要一张晶体管的输出特性曲线,就可以确定它的最大电压放大倍数了.

性能衡量

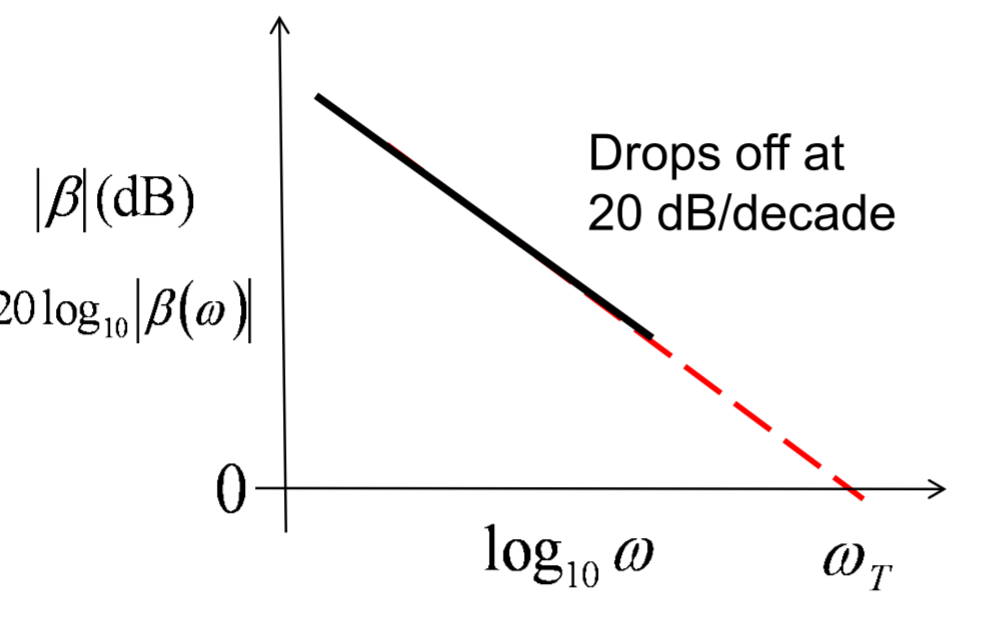

由于晶体管中存在电容部分,会导致相位的延迟,因此它的放大倍数随着信号频率的提高而下降,而当频率增加到一个临界值时,放大倍数将变为1. 我们将这个频率称作晶体管的增益宽带积 \(f_T\) (Gain-bandwidth product),这个量衡量了晶体管的高频性能. 若增益宽带积为1 MHz,它意味着这个晶体管放大器最高可以以1 MHz的频率工作而不至于使信号失真,如果频率继续提高,那么晶体管的性能已经无法跟上了.

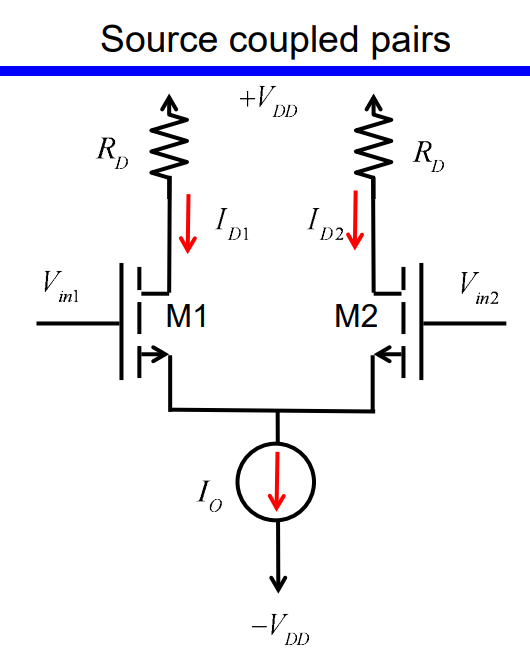

很多射频器件,包括华为希望优化的一些器件,都采用了共源极的设计,在这种结构中器件的匹配性很重要,为了让这种器件能正常地运行,我们希望两侧的晶体管具有相同的特征,因为很小的差别也会降低电路的整体性能.